Intelは、同社の受託製造部門となる「Intel Foundry」の年次イベント「Intel Foundry Direct Connect」を、4月29日(現地時間)にアメリカ合衆国カリフォルニア州サンノゼ市にあるサンノゼコンベンションセンターにおいて開催した。

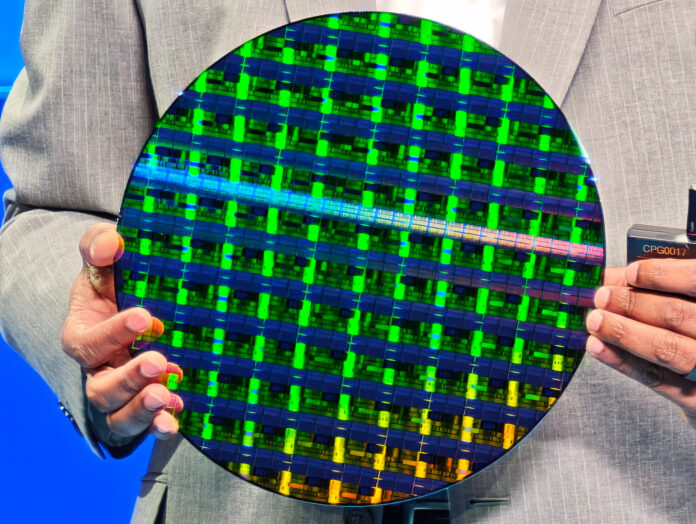

イベントは、Intel Foundryが提供する半導体受託生産サービスを既に利用している、あるいは将来利用する計画がある顧客企業が対象で、前工程(ウェハ生産工程)と後工程(パッケージ封入工程)、それに関するロードマップのアップデートなどが行なわれた。

Intel 18Aで製造されるPanther Lakeは年内投入開始

次いでステージに登壇したIntel 上席副社長 兼 Intel Foundry テクノロジー・製造部門 CTO/COO ナガ・チャンドラシーカラン氏は、より詳細な同社のプロセスノードや先進パッケージング技術に関して現状やロードマップに関する説明を行なった。

この中でチャンドラシーカラン氏は、900億ドルの同社のIntel Foundryへの投資のうち、180億ドルはプロセスノードや先進パッケージング技術などの開発費やされたと説明し、この4年間で着実に技術の開発が進んだと説明している。Intelは、4Y5N(4Year、5Node、4年間で5つのノード開発)という4年間で5世代のプロセスノードを開発するという戦略を推し進めており、今年生産に入るIntel 18Aはその最後のピースとなるノードで、Intel Foundryが本格的に受託生産ビジネスを展開する上で重要なプロセスノードとされている。

Intel 18Aでは2つの新しい技術が導入される。1つは4D形状のゲートになるRibbonFET(いわゆるGAA)で、もう1つがPowerViaの名称で知られる裏面電力供給。いずれも最先端の技術となり、性能や消費電力などの点で競合他社のプロセスノードに比べて高い競争力を持つことが期待されている。

なお、Intel 18Aは、Intel自身の製品で次世代のCore Ultraになる予定のPanther Lakeに利用される計画。タンCEOは「Panther Lakeは今年(2025年)中にいくつかのSKUが投入され、残りは来年(2026年)に投入される計画だ」と、先日の四半期決算で明らかにされたスケジュールを今回も繰り返して説明した。

第2世代のRibbonFET/PowerViaとなるIntel 14A、High NA EUVを使わない選択肢も用意

さらに、同社のプロセスノードおよび先進パッケージ技術のロードマップを更新した。今回追加されたのは、Intel 18Aのバリエーションになる「Intel 18A-PT」、Intel 14Aのバリエーションとなる「Intel 14A-E」の2つだ。

Intel 18A-PTは、Intel 18A-PにTSV(貫通ヴィア)の機能を追加したもので、ほかのダイとより広帯域で通信することができるようになるため、AI用のチップをチップレットで構築する時に最適なプロセスノードになると説明されている。同じTSVの仕組みを採用しているIntel 3-Tと比較してチップ密度が20~25%改善し、電力も25~35%削減され、さらにダイ間の帯域幅の密度が9倍になると説明されている。

2027年にリスク生産が予定されているIntel 14Aでは、第2世代のRibbonFET(RibbonFET2)、第2世代のPowerViaが実装され、Intel製品としては初めてHigh NA EUVに対応。Intel 18Aと比較して電力効率は15~20%向上し、チップ密度は1.3倍になるという。チャンドラシーカラン氏は、このIntel 14AのHigh NA EUVがオプションであることを明らかにし、顧客がHigh NA EUVを選択しない場合には、Intel 3/4で使われたLow NA EUVを利用して設計して、生産することが可能だと説明した。

そのIntel 14AのバリエーションとしてIntel 14A-Eが用意され、RibbonFETにIntelが「Turbo Cell」と呼んでいる新しいセル形状が導入され、より高いクロック周波数などを実現することが可能になると説明された。

パッケージ技術に関しては、Intelが既に提供しているEMIBの拡張版となるEMIB 3.5D、Foverosの拡張版となるFoveros-R、Foveros-B、Foveros Direct 3Dなどの新技術を今後追加していくことを説明した。

Views: 0